A Peer Reviewed Research Journal

# IMPLEMENTATION OF 1-BIT LOW POWER FULL ADDER USING CADENCE TOOL

Dr. G. SUJATHA<sup>1</sup>, GADE ANIL KUMAR<sup>2</sup>, CHINNAMANNA YATHISH<sup>3</sup>, BILLU SISINDRI<sup>4</sup>, EDIGA VIJAYANAND GOUD<sup>5</sup>, BUKKE SAI PRASANTH NAIK<sup>6</sup>

<sup>1</sup>Assosiate Professor, Dept. of ECE, S V College of Engineering, Tirupati, A.P, India. <sup>23456</sup>B.Tech Students, Dept. of ECE, S V College of Engineering, Tirupati, A.P, India.

### ABSTRACT

This paper presents a novel low-power majority function-based 1-bit full adder that uses MOS capacitors in its structure. The power consumption and general characteristics of an adder are then compared against low power adders, the Transmission Gate fullAdder (TGA) and the conventional CMOS full adder. The circuits simulated using CADENCE tool 180nm CMOS process technology. Analysis of performance and efficiency of 1-bit full adder cell designs is carried out for different parameters like average power, supply voltage and transistor count is done. The average power for CMOS technology for 180nm is 209.2uW and for Transmission gate technology for 180nm is 164.4uW. It is observed that within a given logic style, as the technologydecreases the average power decreases with decrease in the area for a constant supply voltage of 5V. It is observed that less power is consumed by transmission gate based 1-Bit full adder than the conventional CMOS 1-Bit full adder.

Keywords: Low-power Full-adder, Low-power CMOS design, Transmission Gate fullAdder.

### 1. INTRODUCTION

With the continuously increasing chips complexity and number of transistors, circuits power consumption is growing as well. Low power circuits have been major design challenge in VLSI technology. Technology enhancements reduce the area for a single chip and increase the number of transistors on a single dice. High number of transistors on single chip leads to high power dissipation. The most conventional one is complementary CMOS full-adder (C-CMOS). It is based on regular CMOS structure with pull-up and pull-down transistors and has 28transistors.

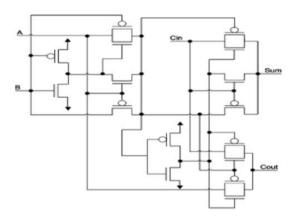

The Transmission Gate Full-Adder (TGA) is proposed. It is based on transmission function theory and transmission gates and has 16 transistors. Transmission gates consists of a PMOS

Crossref

transistor and an NMOS transistor that are connected in parallel.

In this paper a novel full adder circuit is introduced which designed by using inverters and transmission gate. This full adder having simple structure and reduced power consumption in comparison to another designs. The reduction in power consumption due simple structure of circuit and decreased number of transistors used in the circuit.

## 2. LITERATURE REVIEW OF FULL ADDER

The most conventional one is complementary CMOS full-adder (C-CMOS). It is based on regular CMOS structure with pull-up and pull-down transistors and has 28 transistors. Another existing system Transmission Gate Full-Adder (TGA) presented in [8] contains 20 transistors. The Transmission Gate Full-Adder (TGA) is proposed. It is based on transmission function theory and transmission gates and has 16 transistors.

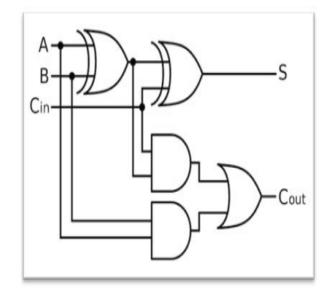

The circuit diagram of a 3-bit full adder is shown in the figure. The output of XOR gate is called SUM, while the output of the AND gate is the CARRY. The AND gate produces a high output only when both inputs are high. The XOR gate produces a

#### A Peer Reviewed Research Journal

high output if either input, but not both, is high. The truth table of 3-bit full adder is given. The 3-bit full adder circuit has a provision to add the carry generated from the lower bits.

The expression for SUM and CARRY is given by,

SUM=A  $\oplus$  B  $\oplus$  Cin = A'B'Cin' + A'BCin' +AB'Cin' +ABCin

$CARRY = AB + Cin (A \bigoplus B) = AB$

+ ACin + BCin = AB + Cin(AB' + A'B)

#### Fig 1. Full Adder Circuit

**Table1: Full Adder Truth Table**

| inputs |   |     | Outputs |       |

|--------|---|-----|---------|-------|

| Α      | В | Cin | Sum     | Carry |

| 0      | 0 | 0   | 0       | 0     |

| 0      | 0 | 1   | 1       | 0     |

| 0      | 1 | 0   | 1       | 0     |

| 0      | 1 | 1   | 0       | 1     |

| 1      | 0 | 0   | 1       | 0     |

| 1      | 0 | 1   | 0       | 1     |

| 1      | 1 | 0   | 0       | 1     |

| 1      | 1 | 1   | 1       | 1     |

## 3. EXISTING METHOD

#### **Conventional CMOS Full Adder:**

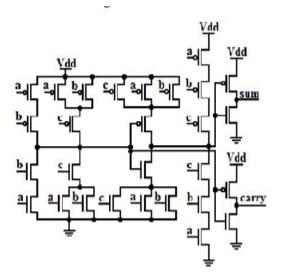

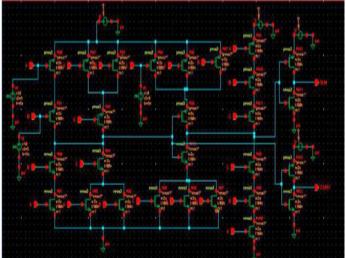

The 1-bit conventional CMOS full adder cell is shown in Fig2. The Complementary MOS Logic Style consists of Pull-Up Network (PUN), which has PMOS transistors and the Pull-Down Network (PDN), which consists of NMOS transistors. The Pull-Up Network connects the output of the gate with Vdd whenever the output of the gate is high. The Pull-Down Network connects gate output and GND when the gate output is low. This logic style consists of 28 transistors.

Fig 2:1-Bit Conventional CMOS Full Adder

A Peer Reviewed Research Journal

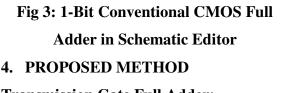

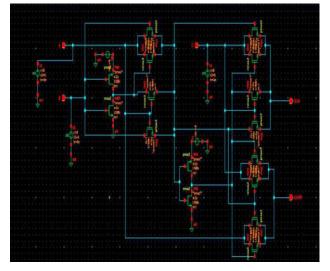

### **Transmission Gate Full Adder:** The TG full adder [8], shown in Fig. 3, is based on transmission gates and introduced for its low power dissipation [4]. As in the case of the LP circuit, cascading full adders leads to an overall propagation delay roughly proportional to, which becomes excessive for long chains of full adders. This drawback is solved in the TG drivcap [6]. Output buffers which interrupt the transmission gate chain when cascading full adders added.The of are use transmission gates enables the circuit to have high speed and low power dissipation.

2581-4575

Crossref

Fig 4: 1-Bit Transmission Gate Full Adder in Schematic Editor

#### Adder

# 5. METHODS OR TECHNIQUES USED

The Cadence tool kit consist of several programs for different applications such as schematic drawing, layout, verification, and simulation.Cadence is a leading Electronicdesign automation (EDA) A Peer Reviewed Research Journal

software.Cadence Virtuoso Analog Design is used for design and simulation which is the advanced design and simulation environment for the Virtuoso Platform.

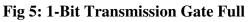

### 6. SIMULATION RESULT

Simulation results performed are by SPECTRE in Virtuoso, Cadence at 180nm CMOS process with the 5V of input voltage and supply voltage. The proposed circuit 1-Bit TransmissionGate Full Adder evaluated and compared to the 1-Bit Conventional CMOSFull Adder circuit. The power obtained of the designs are summarized in the Table 2 for 5V voltage and loads at a fixed input rise and fall time of 5nm. The simulation analysis is carried out with three inputs (A, B, C) and two outputs (Sum and Carry) of Full Adder.

Fig 6: Output Waveforms of Full Adder

75 🗖

### Table2: Simulation Result

Crossref

| S.No | Parameter      | CMOS Full Adder | TGL Full Adder |

|------|----------------|-----------------|----------------|

| 1.   | Technology     | 180nm           | 180nm          |

| 2.   | Supply Voltage | 5V              | 5V             |

| 3.   | Power          | 209.2uW         | 164.6uW        |

### 7. CONCLUSION

Design and simulation of optimized low power 1-bit CMOS and TGLfull adder has been done at 180nm Technology.Low power consumption is preferred in V.L.S.I systemsowing to theirgreater reliability. Cadence virtuososimulations have been performed to evaluate the fulladder cell. In this paper, theperformance of 1-Bit full adder using CMOS and Transmission gate logic styles are compared and analyzed for the parameters like average power supply voltage,transistor count. Also. it is observedthat for one given technology the transmission gate based 1-Bit adder has lower average power, less transistor countand smaller area than the CMOS based 1-Bit full adder circuits.

#### 8. FUTURE SCOPE

In Future, there is Scope for an area efficient, low power and high speed 1-bit full adder by reducing number of transistors such as 10T, 8T, 6T.By the reduction in transistors can produces full swing out signals, which implies this adder has a good driving capability. A prototype of this proposed cell(10T) is built using a 0.6 um CMOS process with single polysilicon and double metal interconnections. Therefore, the cell size of 10T cell is smaller than TGL (the saving in area is equal to 40%)and CMOS cell (the saving in area is equal to 50%).

A Peer Reviewed Research Journal

### 9. REFERENCES

[1] Kavitha Khare, Krishna Dayal Shukla, "Design a 1-bit Low Power Full Adder by using Cadence Tool", AIP Conference Proceedings 1324, 373 (2010).

[2] K. Navi, M. Maeen, V. Foroutan, S. Timarchi, O. Kavehi, "A Novel low-power full-adder cell for low voltage", Integration, the VLSI Journal (2009)10.1016/j.vlsi.2009.02.001.

[3] Y.Jiang,A.Al Sheraidah, Y. Wang, E. Sha,J. Chung, "A novel multiplexer-based low-power full adder",IEEE Transactionson Circuitsand Systems—II: Express Briefs 51(7)(2004July).

[4] Deepa Sinha.; Tripti Sharma.; "Design and Analysis of Low Power 1-bit Full Adder Cell," 3rd International Conference on Electronics Computer Technology (ICECT),

2581-4575

Crossref

IEEE vol., no 2., pp.303 – 305, 8-10 April 2011.

[5] Hamid Reza Naghizadeh.; Mohammad

Sarvghad.; "Design of Two High

Performance 1-Bit CMOS Full Adder

Cells", International Journal of Computing

and Digital Systems, vol., no 1., pp. 47 – 52,

2013.

[6] Subodh Wairya, Rajendra Kumar Nagaria, Sudarshan Tiwari, "New Design methodologies for high-speed mixed-mode CMOS full adder circuits ", International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011.

[7] Keivan Navi.; Omid Kavehei;"Low-Power and High-Performance 1-Bit CMOSFull- Adder Cell", Journal of Computers, Vol. 3, No. 2, February 2008. A Peer Reviewed Research Journal

[8]N. Weste, K. Eshraghian, "Principles of CMOS VLSI Design": A System Perspective, Addison-Wesley, Reading, MA, 1993.

[9] Shivani Sharma, Gaurav Soni, "Comparative study of finFET based 1-bit full adder cell implemented using TG And CMOS logic styles at 10, 22 And 32nm", IOSR Journal of VLSI and Signal Processing (IOSR-JVSP), Volume 6, Issue 1, Ver. I (Jan. -Feb. 2016).

[10] S.M. Kang and Y.Leblebici, "CMOS digital integrated circuits analysis and design", McGraw-Hill, New York, USA-2003.