A Peer Reviewed Research Journal

# DESIGN OF THE RADIX BASED FIR FILTER WITH AREA EFFICIENT

<sup>1</sup>MR. CH. VENKATESWARLU, <sup>2</sup>MR. V. VIJAYA KUMAR

<sup>1,2</sup>Assistant Professor, Department of Electronics and Communication Engineering, Narsimha Reddy Engineering College, Secunderabad, TS, India. chvenkateswarlu@nrcmec.org, v.vijaykumar@nrcmec.org

#### **ABSTRACT**

There is a gigantic ubiquity with quick progression in the innovation identified with the part of the execution identified with the number framework arranged regarding the paired based excess. FIR channel is the core of the computerized flag processor. The yield of the FIR channel is got processed by the assistance of the reaction situated procedure of the limited motivation based parameter in a very much arranged manner by the assistance of the activities identified with the execution parts of the gathering took after by the property of the augmentation individually. Here another method is composed by a well successful system situated technique where the execution of the channel is completed with the assistance of the calculation identified with the radix-256 introduction in a well powerful system and the execution of the number juggling in view of RB. Here, by the system of the encoding with the radix 256 stall's calculation in a very much situated manner, there is an aggregate diminishment in the unpredictability of the framework taken after by the perspective in the diminishment of number of halfway item pushes by 8 overlay. The RB option is actualized to include the incomplete item pushes without convey proliferation which brought about speedier usage. A change in the outcomes has been watched. The execution is seen to be speedier. Execution of this FIR channel is done in XILINX ISE 12.1 ported into SPARTAN 6 FPGA. Investigations have been directed on the show technique and various investigations have been made where there is a precise assessment of the execution.

Keywords: Multiplying circuits, modified Booth encoding, pre-encoded multipliers, VLSI implementation.

### 1. INTRODUCTION

There is a fast headway in the framework as for the correspondence situated viewpoint. Creators of [2] to [5] executed FIR channels with discrete coefficient esteems. Creators of [9] composed FIR filer in course shape. Creators of [10] proposed CSHM calculation for calculation of FIR channel. Creators [1] executed a 11 tap FIR channel. The display work is a FIR channel with 16 taps which

has better reaction. The channel is executed with Radix-256 corner encoding took after by RB expansion. By this the many-sided quality of the framework is lessened to a compelling level. Here the methodology is in view of the acknowledgment based viewpoint identified with the low power took after by the quick speed. Channel identified with the limited drive related procedure plays a noteworthy productive part for the

Crossref

execution of the flag handling wonders separately.

### 1.1 Block Diagram

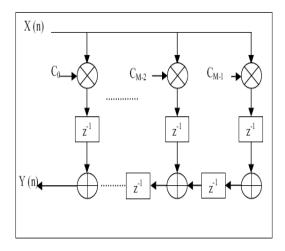

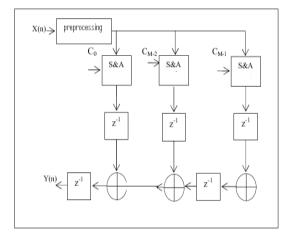

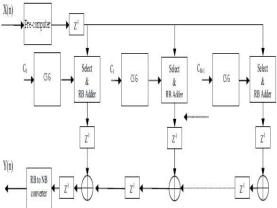

The following are exhibited the general square graph of FIR channel, piece outline of FIR channel with split sharing calculation what's more, the square graph with radix-256 corner multiplier and RB expansion for a 16 tap FIR channel.

Fig 1: Shows the general implementation of FIR filter.

Fig 2: Shows the implementation FIR filter with split sharing multiplier (16 TAP)

### A Peer Reviewed Research Journal

Fig 3: Shows the design structure withradix-256 booth encoding and RB addition for a 16 tap FIR filter.

#### 2. METHODOLOGY

In this paper a technique is planned with a well powerful structure situated methodology in a well viable way where there is a change in the execution of the framework took after by the exact result. There is a gigantic challenge for the present technique where it should precisely break down the issues identified with the few past techniques in a well viable way taken after by the exact examination of the hypothetical part of the outline arranged parameters of the present framework. In the present work the FIR channel is actualized in two techniques and looked at. In technique 1, the split sharing multiplier, the information is preprocessed to get the odd products of contribution from 1X to 15X. The coefficient is partitioned into 4 sections and each part duplicated the info independently. relative items are duplicated with the positional esteems and added to get the multiplier yield. Each increase is done by reasonably moving the information. The

Crossref

items from different duplicated units are reasonably deferred and added to get the channel yield. In the technique 2, Radix-256 corner encoding with RB expansion is done for a 16 tap FIR channel. The info is preprocessed to get the odd products from 1X to 15X. They are additionally prepared to get the products from - 128X to +128X. The select and include unit chooses reasonable two values out of them and believers to RB shape. These two fractional item pushes are added to get the multiplier yield in RB frame. The multiplier yields are reasonably postponed and added to get the last channel yield. The outcomes got in the two techniques are thought about and found that there is a considerable change in the execution of the channel actualized with Radix-256 corner encoding and RB expansion when contrasted with the one with split sharing multiplier. Here the present technique is viable and effective in wording of the usage based technique as it does not include any convey proliferation for Additionally expansion. there no augmentation immediate included and increases are completed by appropriately moving the input. This decreased the computational unpredictability and furthermore the postponement from input to yield. We at long last infer that the show the issues technique totally overcome identified with the few past techniques and enhance the execution of the framework in a proficient way. Here the execution of the present strategy is appeared in the above figures as the piece outlines or the circuit association portrayal and clarifies in a brief elaborative way individually.

### A Peer Reviewed Research Journal

#### 3. EXPECTED RESULTS

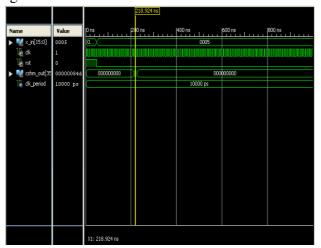

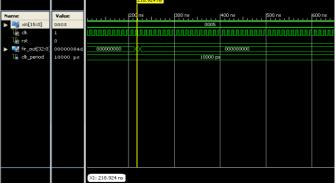

A ton of investigation is made on the introduce outlined strategy in light of the limited drive reaction of the radix-256 based technique in a well compelling way taken after by the gigantic number of the calculations connected on the huge number of the informational indexes. The defer execution is seen to have considerably moved forward. The reproduction comes about acquired in both the techniques are given beneath.

Fig 4: Simulation results of split sharing Multiplier

Fig 5: shows the simulation results of the present method implementation based strategy (1) For split sharing FIR filter and (2) for Radix-256 booth encoding with RB addition.

#### 4. CONCLUSION

In this paper a 16 bit 16 tap FIR channel is actualized with Radix-256 stall encoding and RB expansion, which has indicated significant change over the split sharing multiplier and the other techniques. This has demonstrated low deferral from contribution to yield and thus is exceedingly valuable for a reasonable execution. This is the quickest technique for execution. We at long last infer that the plan situated parameters of the radix 256 plays a great powerful part for the change in the execution based system took after by the exact examination.

### **REFERENCES**

- S.K.Sahoo, Srinivasa Reddy K, "A High Speed FIR filter Architecture based on Novel Higher Radix algorithm" 2012 25thIEEE International Conference on VLSI Design.

- 2. Y. C. Lim, S. R. Parker, and A. G.Constantinides, "Finite word length FIR filter design using integer programming over a discrete coefficient space," IEEE Trans. Acoustics, Speech Signal Processing, vol. ASSP-30, pp. 661–664, Aug. 1982.

- 3. Y. C. Lim and S. R. Parker, "FIR filter design over a discrete power-of two coefficient space," IEEE Trans. Acoustics, Speech Signal Processing, vol. ASSP-31, pp. 583–591, June1983

- 4. H. Samueli, "An improved search algorithm for the design of multiplier less FIR filter with powers-of-two coefficients," IEEE Trans. Circuits Syst., vol. 36, pp. 1044–1047,July 1989

### A Peer Reviewed Research Journal

- 5. Hai Huyen Dam, Cantoni A., Kok LayTeo, Nordholm S.,"FIR Variable Digital Filter With Signed Power-of-Two Coefficients, "IEEE Transactions on Circuits and Systems I, Volume: 54, Issue: 6, pp. 1348 - 1357, June2007.

- 6. Mustafa Aktan, ArdaYurdakul, and GünhanDündar,"An Algorithm for the Design of Low- Power Hardware-Efficient FIR Filters," IEEE Transactions on Circuits and Systems I, VOL. 55, NO. 6, pp. 1536-1545 JULY 2008

- 7. N. Sankarayya, K. Roy, and D. Bhattacharya, "Algorithms for low power and high speed FIR filter realization using differential coefficients," IEEE Trans. Circuits Syst., vol. 44, pp. 488–497, June 1997.

- 8. Vinod A.P., Singla A., Chang C.H., "Low power differential coefficients-based FIR filters using hardware-optimized multipliers, "IET, Circuits, Devices & Systems, Volume: 1Issue:1, pp.13-20, February 2007.

- 9. Dong Shi, Ya Jun Yu, "Design of Discrete-Valued Linear Phase FIR Filters in Cascade Form," IEEE Transactions on Circuits and Systems I, Volume: 58, No. 7, pp. 1627-1636, July 2011.

- 10. Jongsun Park, Woopyo Jeong, Hamid Mahmoodi Meimand, Yongtao Wang, Hunsoo Choo, Kaushik Roy, "Computation sharing programmable FIR filter for low-power and high-performance applications" IEEE Journal of Solid-State Circuits. 2004, 39: 348-357.

- A Peer Reviewed Research Journal

- 11. Avizienis, "Signed-digit number representation for fast parallel arithmetic," IRE Trans. Electron. Computer., vol.EC-10, pp.389-400, Sept.1961.

- Hiroshi Makino, Yasunobu Nakase,

Hiroaki Suzuki, Hiroyuki Morinaka,

Hirofumi Shinohara, and Koichiro

Mashiko, "An 8.8-ns54 x 54-Bit multiplier with high speed redundant binary architecture," IEEE J. Of Solid State Circuits, Vol.31, No.6, pp. 773-783, June 1996.